Суммирующий счетчик

Курсовой проект по микросхемотехнике цифровых интегральных схем.

«Суммирующий счетчик»

Вариант 9.

Содержание

1. Техническое задание.

2. Задание на схемотехническую часть работы.

3. Теоретические сведения.

3.1 Триггеры. Общие сведения.

3.2 Тактируемые триггеры.

3.3 Счетные триггеры.

3.4 Счетчики. Общие сведения.

3.5 Счетчики с последовательным переносом.

4. Логическое моделирование.

4.1 Моделирование TV-триггера.

4.2 Моделирование суммирующего счетчика

5. Базисные вентили.

5.1 Предварительный расчет параметров транзисторов.

5.2 Схемотехническое проектирование.

5.3 Топологическое проектирование.

6. TV-триггер.

6.1 Схемотехническое проектирование.

6.2 Топологическое проектирование.

7. Суммирующий счетчик.

7.1 Схемотехническое моделирование счетчика.

7.2 Топологическое проектирование.

7.3 Анализ и корректировки.

8. Расчет межсоединений и паразитных емкостей.

9. Расчет потребляемой мощности.

Выводы

Список использованной литературы

1. Техническое задание.

1) Используя параметры эквивалентного логического элемента, разработанного в предыдущем КП по курсу «Компьютерное моделирование интегральных приборов», спроектировать схему триггера с динамическим управлением (фронтом или срезом синхросигнала) в соответствии с заданным вариантом. Результатом проектирования является схема, выполняющая заданную по варианту логическую функцию для указанной рабочей частоты при минимальной величине нагрузочной емкости.

2) Выбрать по литературным источникам на базе спроектированного триггера, схему устройства, реализующего заданную логическую функцию (регистра, счетчика, делителя частоты и т.д.) с многоразрядными логическими переменными. Число разрядов не менее 8, число транзисторов в устройстве - не менее 100. При необходимости для реализации логической функции возможны трансформации исходного триггера, например:

- преобразование JK-триггера в Т-триггер и т.п.;

- введение дополнительного логического управляющего сигнала сброса информации и выборки (установки);

- осуществление коррекции топологических размеров исходного логического элемента и связанных с этим времен задержки на логических вентилях. При необходимости выполняется перерасчет схемы триггера при помощи программы SPICE;

- разработка топологического эскиза базовой триггерной схемы с применением измененных топологических вариантов библиотечных элементов.

3) Разработать устройство по полузаказному алгоритму проектирования, считая исходный триггер библиотечным элементом матрицы.

4) При помощи программы OrCad нарисовать электрическую схему устройства.

5) Провести логическое моделирование разрабатываемого устройства при помощи, например, программы ASKT. В качестве библиотечного элемента использовать вентили из библиотеки ASKT.

6) Выполнить эскизный чертеж топологии устройства, используя разработанный ранее эскиз топологии триггера в виде прямоугольника, подсоединенного к шинам питания, с размерами, координатами входов и выходов в заданном масштабе λ-проектирования. C помощью программы PULT или другого алгоритма.

7) Рассчитать паразитные сопротивления и емкости шин межсоединений (разрешено 2 уровня Al-металлизации) по разработанному топологическому варианту.

· Рассчитать величины паразитных емкостей (Спаp) и сопротивлений (Rnap) шин межсоединений для полученного топологического эскиза схемы. Расчет вести для самых длинных шин, если величины Спар будут меньше 10 фФ, a Rnap - меньше 50 Ом, т.е. tзд.паp< 0,1 пс, то вкладом задержек в шинах разводки в быстродействие схемы можно пренебрегать. В ином случае, соответствующие емкости и сопротивления должны быть включены в электрическую схему для проведения моделирования переходных процессов в проектируемой схеме.

· Определить время задержки в шинах связи, сравнить с временами задержки в схеме триггера, скорректировать рабочую частоту.

· Скорректировать величины емкостей, подсоединенных в качестве нагрузки к выходам триггера с учетом дополнительных топологических емкостных нагрузок от шин разводки, на основании этого сделать перерасчет рабочей частоты и потребляемой мощности триггера и устройства на его основе.

8). Изменяемые параметры:

· Емкость нагрузки устройства из исходного курсового и в 10 раз большая,

· Номинал источника питания 5 и 3,6 В.

9) Рассчитать частоту:

- максимальную,

- рабочую,

- при заданных параметрах выходного импульса,

- для различных вариантов нагрузки.

10) Исследования (бонус):

· неопределенных и запрещенных состояний в триггерах,

· функциональных и логических состязаний.

2. Задание на схемотехническую часть работы

Спроектировать суммирующий счетчик со следующими параметрами:

Технологические параметры:

1. Технологический базис CMOS 0.8MKM-2Metal, напряжение питания 5 В.

2. Пороговое напряжение n-канального транзистора Unпор = 0.8 В.

3. Пороговое напряжение р-канального транзистора Upпор = - 0.8 В.

4. Крутизна n-канального транзистора K0n=110 мкА/В2.

5. Крутизна р-канального транзистора К0р= 36 мкА/В2

6. Рабочая частота 100 МГц.

7. Нагрузочная емкость 0.3 пФ.

3. Теоретические сведения

3.1 Триггеры. Общие сведения

Устройство, имеющее два устойчивых состояния, называют триггером. В триггере два выхода: один – прямой, а другой – инверсный. Потенциалы на них взаимно инвертированы: логическая единица на одном соответствует логическому нулю на другом. С приходом переключающих (запускающих) сигналов переход триггера из одного состояния в другое происходит лавинообразно, и потенциалы на выходах меняются на противоположные. В интервале между переключающими сигналами состояние триггера не меняется, т. е. он «запоминает» поступление сигналов, отражая это величиной потенциала на выходе, это дает возможность использовать его как элемент памяти.

При лавинообразных переключениях на выходе триггера формируются прямоугольные импульсы с прямоугольными фронтами. Это позволяет использовать триггер для формирования прямоугольных импульсов из напряжения другой формы (например, из синусоидального). При двух последовательных переключениях триггера на выходе формируется один импульс, т. е. триггер можно использовать в качестве делителя частоты переключающих сигналов с коэффициентом, равным двум.

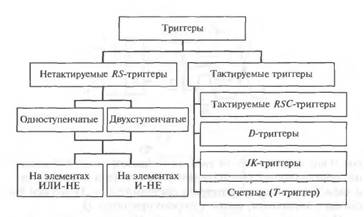

Различают нетактируемые и тактируемые триггеры. Нетактируемый (асинхронный) триггер может менять свое состояние переключающими сигналами в любое время. Тактируемый (синхронный) триггер переключается синхронно с поступлением специального тактирующего импульса. Классификация триггеров приведена на рисунке 3.1.1.

Промышленность выпускает разнообразные типы триггеров в интегральном исполнении. Кроме того, их можно выполнить на цифровых интегральных микросхемах, операционных усилителях и транзисторах.

Рисунок 3.1.1. Классификация триггеров

3.2 Тактируемые триггеры

На входы логического элемента или устройства сигналы не всегда поступают одновременно, так как перед этим они могут проходить через разное число элементов с различной задержкой. Это явление описывается как состязание или гонки сигналов. В результате в течении некоторого времени на входах создается непредвиденная ситуация: новые значения одних сигналов сочетаются с предыдущими значениями других, что может привести к ложному срабатыванию элемента (устройства). Последствия гонок можно устранить временным стробированием, когда на элемент, кроме информационных сигналов подаются тактирующие (синхронизирующие) импульсы, к моменту прихода которых информационные сигналы заведомо успевают установиться на входах.

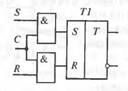

Тактируемый триггер, кроме информационных входов, имеет синхронизирующий (тактирующий, тактовый) вход С; сигналы на информационных входах воздействуют на такой триггер только с поступлением сигнала на синхронизирующий вход. Различают следующие виды тактируемых триггеров: RS-триггеры (рисунок 3.2.1), двухступенчатые RS-триггеры, D-триггеры и JK-триггеры

Рисунок 3.2.1. Тактируемый RS-триггер.

3.3 Счетные триггеры

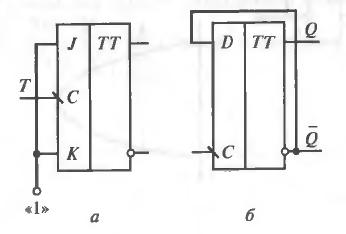

Отличие счетного триггера от остальных состоит в том, что он переключается с поступлением каждого импульса на тактовый вход, называемый в таком триггере счетным.

Счетный триггер можно реализовать на базе JK-триггера. Логическая единица на одном из входов элемента И не определяет потенциал на его выходе, поэтому сочетание J = K = 1 не влияет на выходную характеристику первой ступени триггера. Она получает информацию только с выходов триггера, которая устанавливает ее в положение, когда с приходом счетного импульса начнется очередное переключение – JK-триггер работает в счетном режиме. Реализация счетного режима на JK-триггере приведена на рисунке 3.3.1, а.

Рисунок 3.3.1. Реализация счетного триггера на а) JK-триггере, б) D-триггере

Счетный триггер можно реализовать и на D-триггере (рисунок 3.3.1, б). Если после каждого переключения обеспечить автоматическую смену уровня потенциала на D-входе, то с каждым импульсом на C-входе триггер будет менять свое состояние. Указанная смена потенциала будет осуществляться, если D-вход соединить с выходом ØQ. Вторая перекрестная связь (аналогичная связи в JK-триггере) обеспечивается за счет соединения D-входа с R-входом запоминающей ячейки триггера через инвертор.

3.4 Счетчики. Общие сведения

Счетчики выполняют на запоминающих элементах – триггерах. Он фиксирует число импульсов, поступивших на его вход. В интервалах между ними счетчик хранит информацию об их числе. Совокупность единиц и нулей на выходах n триггеров (выходах счетчика) представляет собой n-разрядное двоичное число, однозначно определяющее количество прошедших на входе импульсов. Поэтому триггеры счетчика называют его разрядами.

Суммирующий счетчик увеличивает свое содержимое на единицу с поступлением каждого входного (счетного) импульса. Вычитающий счетчик аналогично уменьшает свое содержимое на единицу.

Комбинацией суммирующего и вычитающего счетчиков является реверсивный счетчик. У него может быть два входа, на один из которых поступают импульсы, увеличивающие его содержимое (суммирующие импульсы), на другой – вычитающие. Реверсивный счетчик может иметь один вход для суммирующих и вычитающих импульсов, а переключение с одного режима на другой осуществляется в нем сигналом на специальном входе.

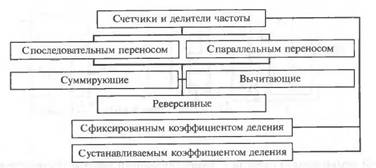

В счетчик может предварительно заноситься число, для чего он имеет специальные входы. Классификация счетчиков и делителей частоты приведена на рисунке 3.4.1.

Рисунок 3.4.1. Классификация счетчиков и делителей частоты

Каждый разряд счетчика может находиться в двух состояниях. Число устойчивых состояний, которое может принимать данный счетчик, называют его емкостью, модулем счета или коэффициентом пересчета.

Одним из основных параметров счетчика является его быстродействие. Оно оценивается минимальным интервалом между двумя соседними импульсами, с поступлением каждого из которых счетчик способен изменить свое содержимое. Счетчик является атрибутом многих цифровых устройств различного назначения. Его можно использовать по прямому назначению – для счета поступающих на его вход импульсов и для деления их частоты следования.

Триггеры счетчика соединяются между собой таким образом, чтобы каждому числу поступивших импульсов соответствовали единичные состояния определенных триггеров. Счетчик, у которого при поступлении входного импульса переключающий перепад передается от предыдущего триггера к последующему, называется счетчиком с последовательным переносом, а когда переключающий перепад на все разряды поступает одновременно (или почти одновременно) – счетчиком с параллельным переносом. Счетчики могут выполняться только на счетных триггерах. О состоянии разряда счетчика судят по потенциалу на прямом выходе триггера.

В большинстве случаев счетчики строятся таким образом, чтобы записываемое в них число было выражено в натуральном двоичном коде. В таком коде «вес» 1 на прямом выходе младшего разряда равен 1, а в каждом последующем разряде вдвое больше, чем в предыдущем.

3.5 Счетчики с последовательным переносом

Первый разряд счетчика, будучи счетным триггером, переключается каждым входным импульсом. Каждый последующий разряд счетчика получает переключающий перепад (1/0 или 0/1) от предыдущего разряда – переключающий перепад распространяется вдоль цепочки триггеров счетчика последовательно.

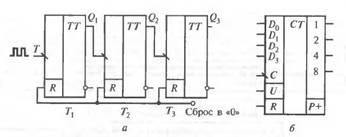

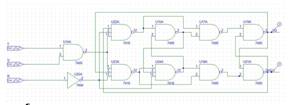

Схема суммирующего счетчика с последовательным переносом приведена на рисунке 3.5.1, а. С поступлением каждого входного импульса число в счетчике увеличивается на единицу. Если в данном разряде присутствует единица, то под воздействием перепада, поступающего от предшествующего, он обнуляется, и единица переносится в следующий разряд. Если же в данном разряде ноль, то в него вписывается единица.

Рисунок 3.5.1. Суммирующий счетчик с последовательным переносом а) схема, б) условное изображение.

На рисунке 3.5.2, б представлено условное изображение 4-разрядного счетчика. На счетный С вход поступают импульсы. Логическая единица на входе К сбрасывает все разряды счетчика в ноль. По входам предварительной установки D0 – D3 в счетчик может быть записано число, его значение должно сопровождаться логической единицей на входе разрешения V. Число, занесенное в счетчик, фиксируется на его выходах двоичным кодом с «весами» разрядов 1-2-4-8. На выходе P+ появляется логическая единица с поступлением на вход 16-го импульса, т. е. вслед за тем, как предыдущими 15-ю импульсами все разряды счетчика были установлены в единицу.

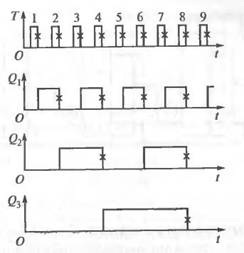

Суммирующий счетчик функционирует по правилам сложения двоичных чисел. Это легко проследить по временной диаграмме, изображенной на рисунке 3.5.2, где крестиками отмечены переключающие перепады 1/0.

Рисунок 3.5.2. Временная диаграмма работы суммирующего счетчика.

Из временных диаграмм можно сделать следующие выводы:

- с наибольшей частотой переключается входной триггер счетчика;

- частота импульсов на выходе каждого триггера вдвое меньше, частоты импульсов на его входе, а n разрядов счетчика делят частоту входных импульсов в 2n раз, таким образом, счетчик является делителем числа входных импульсов с коэффициентом деления (пересчета), равным емкости счетчика Ксч;

- при поступлении на вход суммирующего счетчика 2n импульсов он переполняется: все триггеры устанавливаются в 0 (счетчик обнуляется);

- максимальное число, которое может содержать счетчик, на единицу меньше его емкости N = Ксч – 1 = 2n – 1;

- в момент, предшествующий переключению очередного разряда, все предыдущие разряды счетчика находятся в состоянии 1.

Если в счетчике использованы триггеры, переключающиеся перепадом 0/1, то вход последующего триггера нужно соединить с инверсным выходом предыдущего, на котором формируется этот перепад, когда по основному выходу триггер переключается из 1 в 0. (1)

4. Логическое моделирование

4.1 Моделирование TV-триггера

триггер суммирующий счетчик

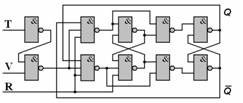

По заданию, необходимо использовать динамический TV-триггер, в качестве базисного. Для этого, модифицируем схему стандартного динамического JK триггера, превратив его в T-триггер, и добавив ему асинхронные входа R и V (сброс и принудительное хранение). В итоге, собранный триггер будет выглядеть следующим образом:

Рисунок 4.1.1. Динамический TV-триггер.

Проведем логическое моделирование TV-триггера в Orcad:

Рисунок 4.1.2. Схема TV-триггера в Orcad.

Результат логического моделирования:

Рисунок 4.2.3. Диаграмма переключения TV-триггера.

Таблица 4.1.1. Таблица истинности TV-триггера.

| V | T | Qn+1 |

| 0 | 0 | Qn |

| 0 | 1 | Qn |

| 1 | 0 | Qn |

| 1 | 1 | ⌐ Qn |

Категории:

- Астрономии

- Банковскому делу

- ОБЖ

- Биологии

- Бухучету и аудиту

- Военному делу

- Географии

- Праву

- Гражданскому праву

- Иностранным языкам

- Истории

- Коммуникации и связи

- Информатике

- Культурологии

- Литературе

- Маркетингу

- Математике

- Медицине

- Международным отношениям

- Менеджменту

- Педагогике

- Политологии

- Психологии

- Радиоэлектронике

- Религии и мифологии

- Сельскому хозяйству

- Социологии

- Строительству

- Технике

- Транспорту

- Туризму

- Физике

- Физкультуре

- Философии

- Химии

- Экологии

- Экономике

- Кулинарии

Подобное:

- Технология цифровой связи

1 Лекция №1. Элементы систем цифровой связи1.1 Функциональная схема и основные элементы цифровой системы2 Лекция №2. Каналы связи и их ха

- Активный полосовой фильтр

- Расчет зеркальной параболической антенны с облучателем в виде конического рупора

- Разработка печатного узла

ВведениеСовременные электронные средства проектируются с использованием интегральных схем высокой степени интеграции и элементной б

- Отопление здания

Общая частьТеплотехника – область науки, техники, занимающаяся вопросами получения и использования тепла.Одновременно с теплотехнико

- Данные дистанционного зондирования Земли как источник информации для баз геоданных

- Инженерные коммуникации

Естественная насыщенность почвы водой, как правило, не совпадает с нужной для роста и развития растений влажностью и во многих случаях

Copyright © https://www.referat-web.com/. All Rights Reserved

referat-web.com Бесплатно скачать - рефераты, курсовые, контрольные. Большая база работ.

referat-web.com Бесплатно скачать - рефераты, курсовые, контрольные. Большая база работ.