Описание процессоров семейства ADSP

1. писание сигнальных процессоров семейства ADSP 2100

Семейство процессоров ADSP-2100 представляет собой совокупность программируемых микропроцессоров с общей структурой, оптимизированную для обработки аналогового сигнала в цифровой форме, а так же для других прикладных целей. Различные микропроцессоры отличаются друг от друга преимущественно типом периферийных устройств, которые дополняют основную структуру. В различных членах семейства могут имеется память, таймер, последовательный и параллельный порты. Кроме того, процессоры ADSP-21msp58/59 включают аналоговый интерфейс для преобразования сигнала звуковой частоты.

1.1. Функциональные модули

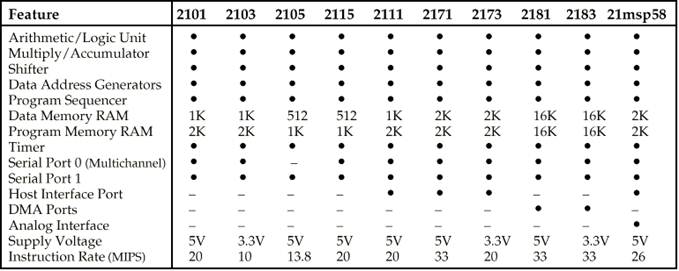

Таблица 1.1 показывает характеристики, которыми обладают отдельные члены семейства.

Таблица 1.1

Computational Units (вычислительный модуль) – каждый процессор семейства ADSP-2100 содержит три полнофункциональных независимых вычислительных модуля: arithmetic/logic unit (ALU) – арифметичиско-логический, multiplier/accumulator (MAC) – накопитель, barrel shifter – сдвиговый расширитель.Все модули оперируют с 16-разрядными словами, а также обеспечивают аппаратную поддержку мультиточности.

Data Address Generators & Program Sequencer (генераторы адресов данных и программа sequencer) – два отдельных генератора адресов обеспечивают адреса для встроенной и внешней памяти. Сдвоенные генераторы адресов данных позволяют процессору генерировать адреса для двух выборок операнда одновременно, что максимизирует производительность.

Memory (память) – в семействе ADSP-2100 применяется архитектура памяти, в которой данные хранятся в секции данных, а в секции программ хранятся как данные так и команды. Все процессоры семейства имеют оперативную память состоящую и этих двух сегментов. Быстродействие внутренней памяти позволяет процессору выбирать два операнда (один из области данных, другой из области программ) в течении одного цикла.

Serial Ports (последовательные порты) – обеспечивают последовательный интерфейс связи с аппаратными средствами, предназначенными для сжатия, хранения и обработки данных. Интерфейс совместим с большим числом известных устройств. Каждый порт может использовать как внутренний таймер, так и внешний. Последовательный порт 0 имеет многоканальные возможности.

Timer – 8-разрядный программируемый таймер/счетчик обеспечивает периодическую генерацию прерываний.

Host Interface Port (главный связной порт) – обеспечивает прямое соединение с главным процессором ЭВМ. Например Motorola 68000, Intel 8051 или другой процессор семейства ADSP-2100 могут быть легко соединены с главным интерфейсом.

DMA Ports (порты DMA) – в ADSP-2181 внутренний (IDMA) и байтовый (BDMA) DMA порты обеспечивают эффективную передачу данных из внутренней памяти и в неё. IDMA порт имеет мультиплексный адрес и 16-битную шину данных. IDMA порт полностью асинхронный данные в него могут записываться, в то время когда ADSP-2181 полностью занят.

Analog Interface (аналоговый интерфейс) – процессоры ADSP-21msp58/59 имеют встроенную схему для цифровой обработки аналогового сигнала. Эта схема содержит АЦП (ADC) и ЦАП (DAC), аналоговые и цифровые фильтры и параллельный интерфейс связи с ядром процессора.

Архитектура семейства ADSP-2100 приспособлена к выполнению задач с помощью цифрового сигнального процессора и построена таким образом, что устройства за один такт могут выполнять следующие действия:

· генерировать следующий адрес программы;

· выбирать следующую команду;

· выполнять один или два шага программы;

· модифицировать один или два указателя адреса данных;

· выполнять вычисление.

В этом же такте процессоры, которые имеют релевантные модули могут:

· принимать и/или передавать данные через последовательный порт;

· принимать и/или передавать данные через главный порт интерфейса;

· принимать и/или передавать данные через DMA порты;

· принимать и/или передавать данные через аналоговый интерфейс.

1.2. Системный интерфейс и интерфейс памяти

В каждом процессоре семейства ADSP-2100 четыре внутренних шины соединяют внутреннюю память с другими функциональными модулями:

- шина адреса;

- шина данных;

- шина памяти программ;

- шина памяти данных.

Внешние устройства могут получать контроль над шинами посредством сигналов предоставления (BR,BG). Процессоры ADSP-2100 могут работать в то время когда шины предоставлены другому устройству, пока не требуется операции с внешней памятью.

Схема начальной загрузки дает возможность автоматической загрузки внутренней памяти после того как ее содержимое было стерто. Это можно осуществлять с помощью интерфейса памяти из EPROM, из главного компьютера, посредством главного порта интерфейса, а так же через BDMA порт процессора 2181. Программы могут загружаться без применения каких-либо дополнительных аппаратных средств.

1.3. Система команд

Процессоры семейства ADSP-2100 используют единую систему команд для совместимости с устройствами с более высокой интеграцией. Микропроцессоры ADSP-2171, ADSP-2181 и ADSP-21msp58/59 имеют ряд дополнительных команд. Система команд позволяет выполнять мультифункциональные команды за один такт процессора, с другой стороны каждая команда может быть выполнена отдельно в своем такте. Ассемблер имеет алгебраический синтаксис, для повышения удобочитаемости легкости кодирования.

1.4. Эффективность сигнального процессора

Сигнальный процессор должен быть не только очень быстродействующим, но удовлетворять некоторым требованиям в следующих областях:

· Быстрая и гибкая арифметика – архитектура процессоров ADSP-2100 позволяет в одном производить такие операции, как умножение, умножение с накоплением, произвольное смещение, а так же ряд стандартных арифметических и логических операций в одном цикле процессора.

· Расширенный динамический диапазон – 40-разрядный аккумулятор имеет восемь резервных бит защиты от переполнения при последовательном суммировании, которые гарантируют, что потери данных быть не может.

· Выборка двух операндов за один цикл – при расширенном суммировании на каждом цикле процессора необходимо два операнда. Все члены семейства ADSP-2100 способны поддерживать обработку данных с двумя операндами, сохранены ли данные в памяти или нет.

· Аппаратные циклические буферы – большой класс алгоритмов обработки цифро-аналоговых сигналов, включая цифровые фильтры требуют наличия циклических буферов. Архитектура семейства ADSP-2100 имеет аппаратные средства для обработки указателя адреса wraparound, что упрощает реализацию круговых буферов.

· Переход по нулю – повторяющиеся алгоритмы наиболее логично выражать через циклы. Программа Sequenser ADSP-2100 поддерживает работу с циклическим кодом с нулем на верху, в объединении со структурой clearest это повышает эффективность системы. Также нет препядствий для работы с условными переходами.

2. Основная архитектура

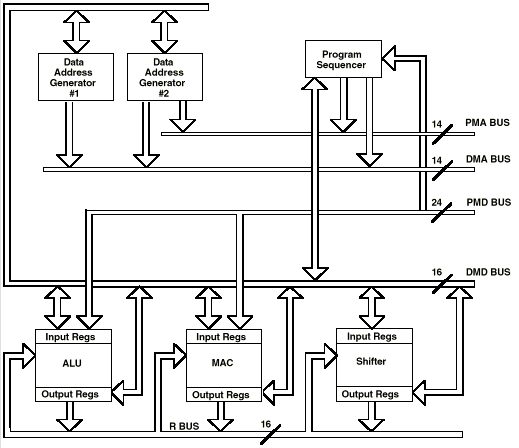

В этом разделе описывается основная архитектура процессоров семейства ADSP-2100, схема которой приведена на рис. 2.1.

2.1. Вычислительные модули

Как уже говорилось выше каждый процессор семейства ADSP-2100 содержит три независимых вычислительных модуля:

- арифметико-логический (ALU);

- умножение с накоплением (MAC);

- расширитель (shiffter).

Эти устройства работают с 16-разрядными данными и обеспечивают аппаратную поддержку мультиточности.

ALU выполняет ряд стандартных арифметических и логических комманд в дополнене к примитивам деления. MAC выполняет одноцикловые операции умножения, умножения/сложения, умножения/вычитания. Shiffter осуществляет логические и арифметические сдвиги, нормализацию, денормализацию и операцию получения порядка, атак же управление форматом данных,разрешая работу с плавоющей точкой. Вычислительные модули размещаются последовательно друг за другом, таким образом чтобы выход одного мог стать входом другого в следующем цикле. Результаты работы модулей собираются на 16-разрядную R-шину.

Все три модуля содержат входные и выходные регистры, которые доступны черех 16-разрядную DMD-шину. Комманда, выполняемые в модулях, берут в качестве операндов данные находящиеся в регистрах ввода и после выполнения записывают результат в регистры вывода. Регистры являются как бы промежуточным хранилищем между памятью и вычислительной схемой. R-шина позволяет результату одного вычисления стать операндом к другой операции. Это позволяет сэкономить время обходясь без лишних пересылок модуль-память.

|

referat-web.com Бесплатно скачать - рефераты, курсовые, контрольные. Большая база работ.

referat-web.com Бесплатно скачать - рефераты, курсовые, контрольные. Большая база работ.