Синтез логической ячейки ТТЛШ

Министерство образования Российской Федерации

Новгородский Государственный Университет

имени Ярослава Мудрого

Кафедра физики твердого тела и микроэлектроники

СИНТЕЗ ЛОГИЧЕСКОЙ СХЕМЫ ТТЛШ

Комплексное задание

по практическим занятиям и лабораторным работам

по дисциплине: «Проектирование и конструирование

полупроводниковых приборов и ИМС»

Выполнил:

студент группы 8033у

__________ А.А. Шишков

Проверил:

к.т.н., доцент кафедры ФТТМ

______________ М.Н. Петров

2000

Синтез принципиальной электрической схемы.

Исходя из технический параметров ИМС приведенных в ТЗ реализуем логическую функцию F=X1+X2X3 на основе логической схемы ТТЛШ (на логическом базисе 2И-НЕ).

Рисунок 1 – Схема логической функции в базисе 2И-НЕ

Таблица 1 – Таблица истинности логической функции

Х1 Х2 Х3 F 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 1

Рисунок 2 – Принципиальная электрическая схема логического базиса 2И-НЕ

Программа расчета блока логического базиса 2И-НЕ на языке программы PSpice.

* Комплексная работа по предмету ПИММС

*Студент группы 8033у

R1 3 12 20k

R2 4 12 8k

R3 5 6 1.5k

R4 7 5 3k

R5 11 10 4k

R6 12 8 120

R7 10 0 1E+9

D1 0 2 D_SH

D2 0 1 D_SH

D3 3 1 D_SH

D4 3 2 D_SH

D5 3 4 D_SH

D6 9 4 D_SH

D7 4 8 D_SH

D8 5 10 D_SH

D9 6 7 D_SH

Q1 4 3 5 Tran

Q2 7 6 0 Tran

Q3 9 4 11 Tran

Q4 8 9 10 Tran

Q5 10 5 0 Tran

.model Tran npn ()

.model D_SH D(IS=1E-11 TT=0)

VIN1 1 0 pulse(0 5 0.01us 0 0 0.03us 0.2us)

VIN2 2 0 5

VCC 11 0 5

.DC vin1 0 5 0.01

.tran 0.001us 0.07us

.probe

.END

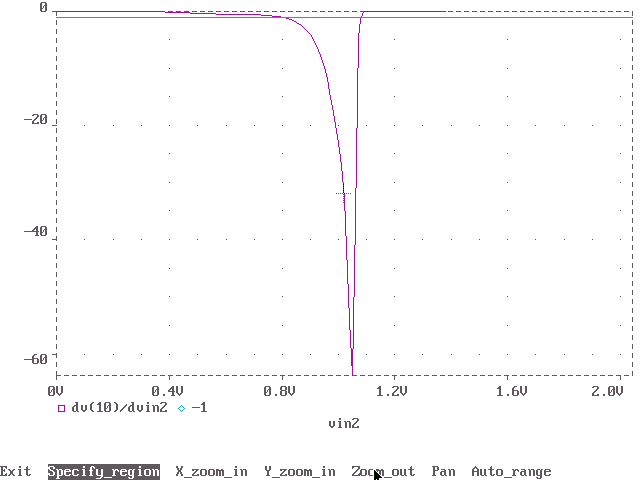

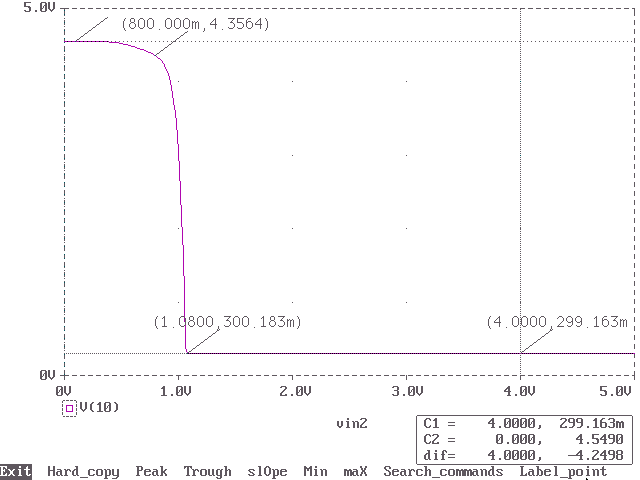

Рисунок 3 - Определение пороговых напряжений

Из графика видно, что U0пор=0,798 В и U1пор=1,08 В.

Рисунок 4 - Передаточная характеристика базового логического элемента 2И-НЕ

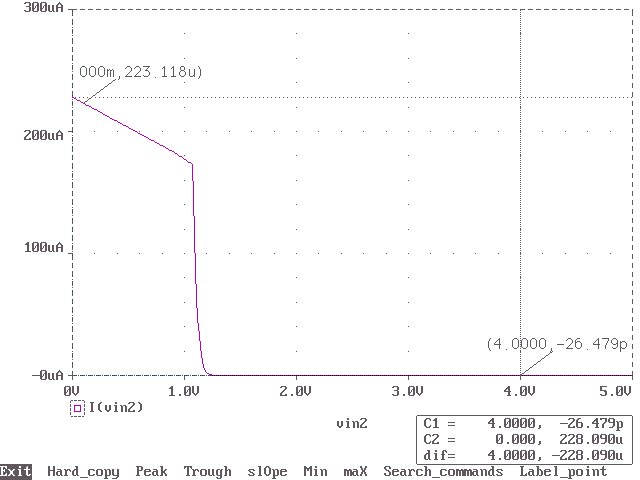

Рисунок 5 - ВАХ на входе логического элемента

Найдены значения I0=0.22 мА и I1=0.026 мкА.

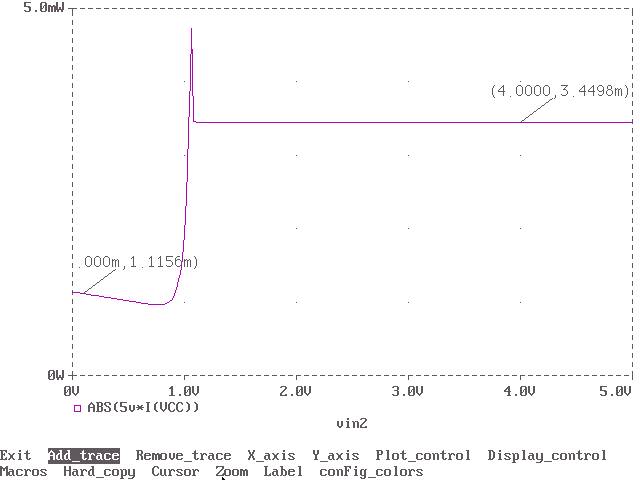

Рисунок 6- Мощность потребляемая логическим элементом

Из графика видно, что Р0=3.45 мВт и Р1=1.12 мВт.

Отсюда находим среднюю мощность:

Рср=( Р0+ Р1)/2=(3.45+1.12)/2=2.285 мВт

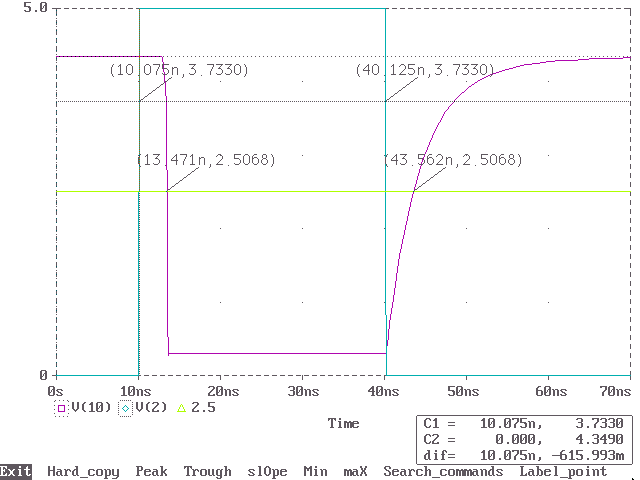

Из рисунка 7 находим t10=3.39 нсек и t01=3.44 нсек.

Находим общее время задержки:

tз=( t10+ t01)/2=(3.39+3.44)/2=3.415 нсек

Рисунок 7 – Временные характеристики логического элемента

Категории:

- Астрономии

- Банковскому делу

- ОБЖ

- Биологии

- Бухучету и аудиту

- Военному делу

- Географии

- Праву

- Гражданскому праву

- Иностранным языкам

- Истории

- Коммуникации и связи

- Информатике

- Культурологии

- Литературе

- Маркетингу

- Математике

- Медицине

- Международным отношениям

- Менеджменту

- Педагогике

- Политологии

- Психологии

- Радиоэлектронике

- Религии и мифологии

- Сельскому хозяйству

- Социологии

- Строительству

- Технике

- Транспорту

- Туризму

- Физике

- Физкультуре

- Философии

- Химии

- Экологии

- Экономике

- Кулинарии

Подобное:

- Синтез управляющего автомата операции умножения младшими разрядами вперед со сдвигом множимого над числами в форме с фиксированной точкой в формате {1,8} для автомата Мура

1. Разработка микропрограммы1.1. Пример1.2. Определение структуры операционного автомата1.3. Разработка граф схемы алгоритма2. Синтез м

- Синтез цифрового автомата управления памятью

В соответствии с заданием в данном курсовом проекте необходимо синтезировать цифровой автомат. После нажатия кнопки ПУСК эта схема дол

- Синтезирование управляющего автомата

Министерство общего и профессионального образованияВологодский политехнический институт Кафедра: АТППДисциплина: ССУКурсовой проект

- Синхронизация SDH сетей

Министерство РФ по связи и информатизацииУральский Государственный Технический Университет - УПИКафедра "ТиСС" Отчетпо производ

- Система дистанционного контроля акустического окружения (шумомер)

Відзив про роботу над дипломним проектом студента гр. ДЗ-92 ФЕЛ Булавка Дмитра Ігоровича на тему «Система дистанційного контролю акустич

- Система наведения ракеты ФКР-1

1. НАЗНАЧЕНИЕ СИСТЕМЫ НАВЕДЕНИЯ И РЕШАЕМЫЕ ЕЮ ЗАДАЧИ. Система наведения ракеты ФКР-1 представляет собой комплекс технических средств, пр

- Система отображения информации

ЗаданиеРазработать алфавитно-цифровое устройство отображения информации телевизионного типа.Исходные данные: Информационная емкость

Copyright © https://referat-web.com/. All Rights Reserved

referat-web.com Бесплатно скачать - рефераты, курсовые, контрольные. Большая база работ.

referat-web.com Бесплатно скачать - рефераты, курсовые, контрольные. Большая база работ.